Entwicklung einer Pipelinearchitektur für einen FPGA-basierten Mikrocontroller

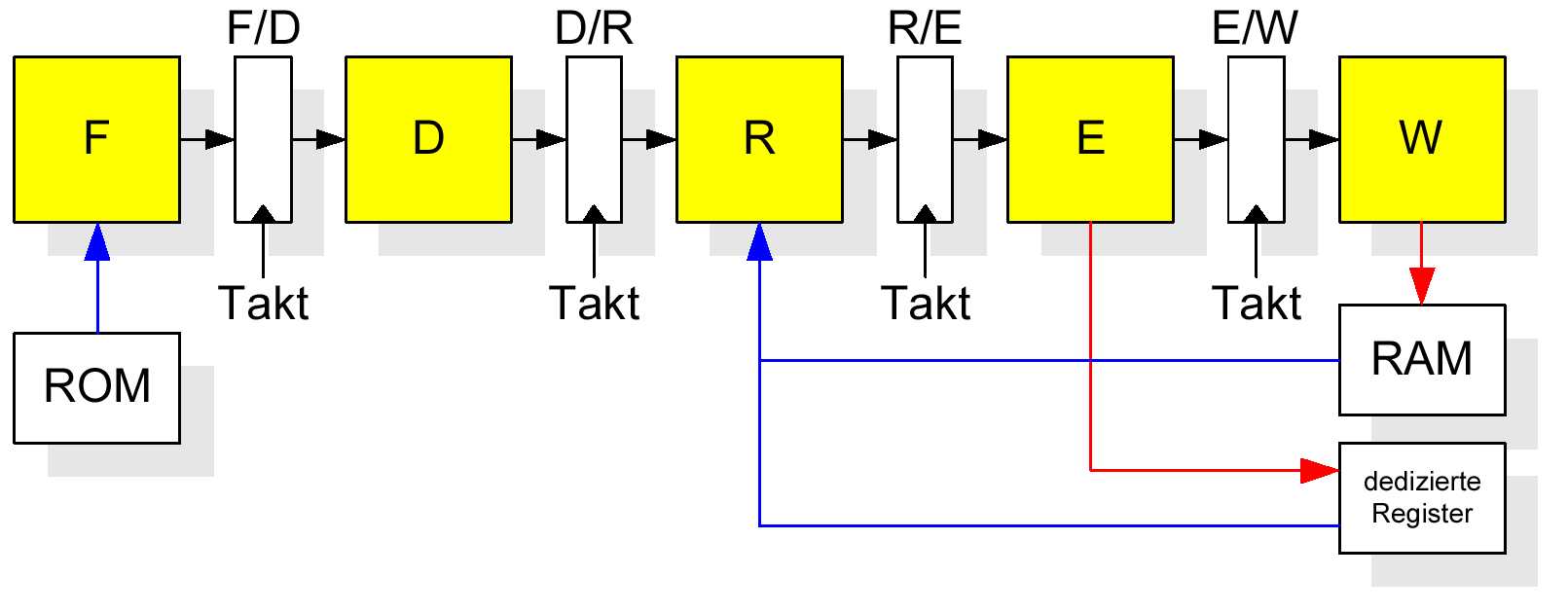

Ziel des Projektes war, eine leistungsfähige Pipelineversion des realisierten PIC-kompatiblen, synthetisierbaren Mikrocontrollerkerns zu entwickeln.

-

Zuerst wurde eine detaillierte Konzeption der Pipelineversion des Mikrocontrollers erstellt. Die Anzahl der Stufen wurde auf fünf festgelegt, was einer max. theoretischen Steigerung der Verarbeitungsgeschwindigkeit von vier entspräche.

-

Die Befehlssatzanalyse ergab die Informationen, welche Befehle/Befehlsfolgen Hasards auslösen (können), was wiederum grundsätzliche Anforderungen für die Implementierung der Pipeline und die Hasarderkennung sowie die Data Forwarding Unit lieferte: Bericht über die Ergebnisse der ersten Projektphase.

-

In der zweiten Phase erfolgten Implementierung und Test sowie Performance-Untersuchungen. Die Ergebnisse und die gute Performance des Pipelined Microcontroller beschreiben im Überblick dieses Poster sowie im Detail die Präsentation und der Konferenzbeitrag zur Embedded World 2009.