Entwicklung eines FPGA-basierten Mikroprozessorkerns

Im Rahmen kleinerer FuE-Projekte entstand ein PIC-kompatibler, synthetisierbarer Mikrocontrollerkern als "IP" für weitere FuE-Projekte und zum Einsatz in der Ausbildung. Der Kern wurde anschließend optimiert und mit einem Debugsystem sowie einem Trace Buffer versehen.

Entwicklung eines Mikroprozessorkerns (erste Version)

-

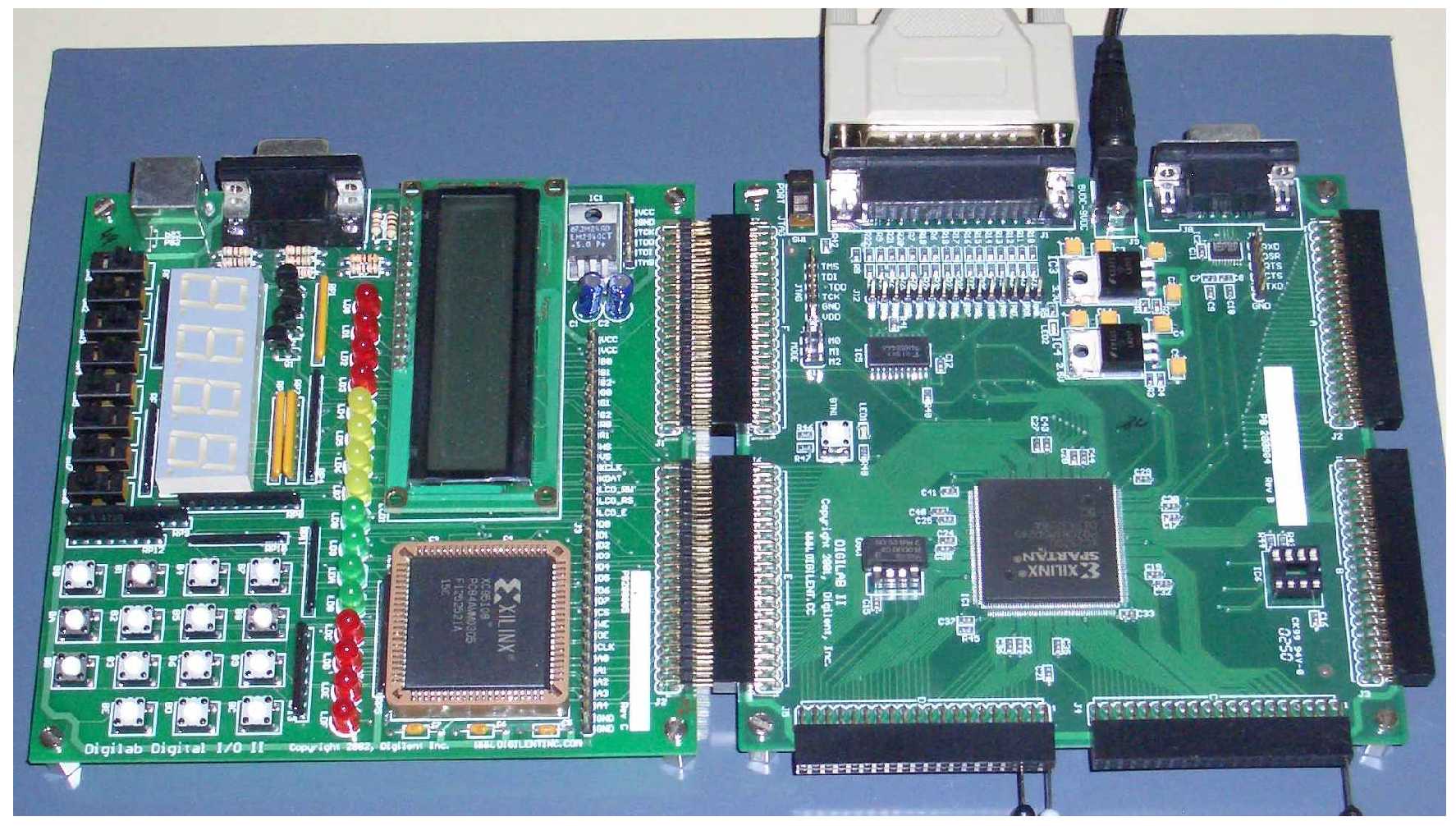

In diesem FuE-Projekt konnte ein kleiner Mikroprozessorkern entwickelt werden, ein adaptierbarer, auf preiswerten FPGA-Modulen implementierbarer Kern, der mit den Mikrocontrollern der sog. PICmicro Mid-Range Family der Firma Microchip weitestgehend kompatibel ist.

-

Die Realisierbarkeit in programmierbarer Hardware ist ein wesentlicher Unterschied zu anderen frei verfügbaren Mikroprozessorkernen, deren Beschreibungen nicht oder höchstens teilweise implementierbar sind.

-

Der Controller erreichte in der ersten Version eine maximale Taktfrequenz von größer 25 MHz. Diese Geschwindigkeit lässt sich noch steigern. Erste Versuche zeigten mögliche max. Taktfrequenzen im Bereich größer 36 MHz. Das Design benötigt in der ersten Version 380 (16%) von 2352 verfügbaren Slices (= 1176 CLBs, Configurable Logic Blocks) im verwendeten Xilinx Spartan II FPGA (XC2S200-5). --> Bericht über die Ergebnisse der ersten Projektphase (Kurzfassung)

Optimierung des Kerns

-

In der zweiten Phase erfolgte eine Optimierung des Kerns hinsichtlich Geschwindigkeit bei gleichzeitig möglichst reduziertem Ressourcenverbrauch. So wurde beispielsweise die ALU bei gleicher Funktion um 40% reduziert. Auch das Modul DECODE konnte deutlich optimiert werden. An Peripheriemodulen kam ein UART hinzu. Die mit einem Xilinx Spartan II FPGA (XC2S200-5) erreichten Taktfrequenzen für den PIC-kompatiblen Mikroprozessorkern liegen über 80 MHz (!). Mit einem Spartan-3-basierten Entwicklungsboard konnten sogar Taktfrequenzen von 100 MHz erreicht werden. --> Bericht über die Ergebnisse der zweiten Projektphase (Kurzfassung) (Langfassung)

Debugsystem

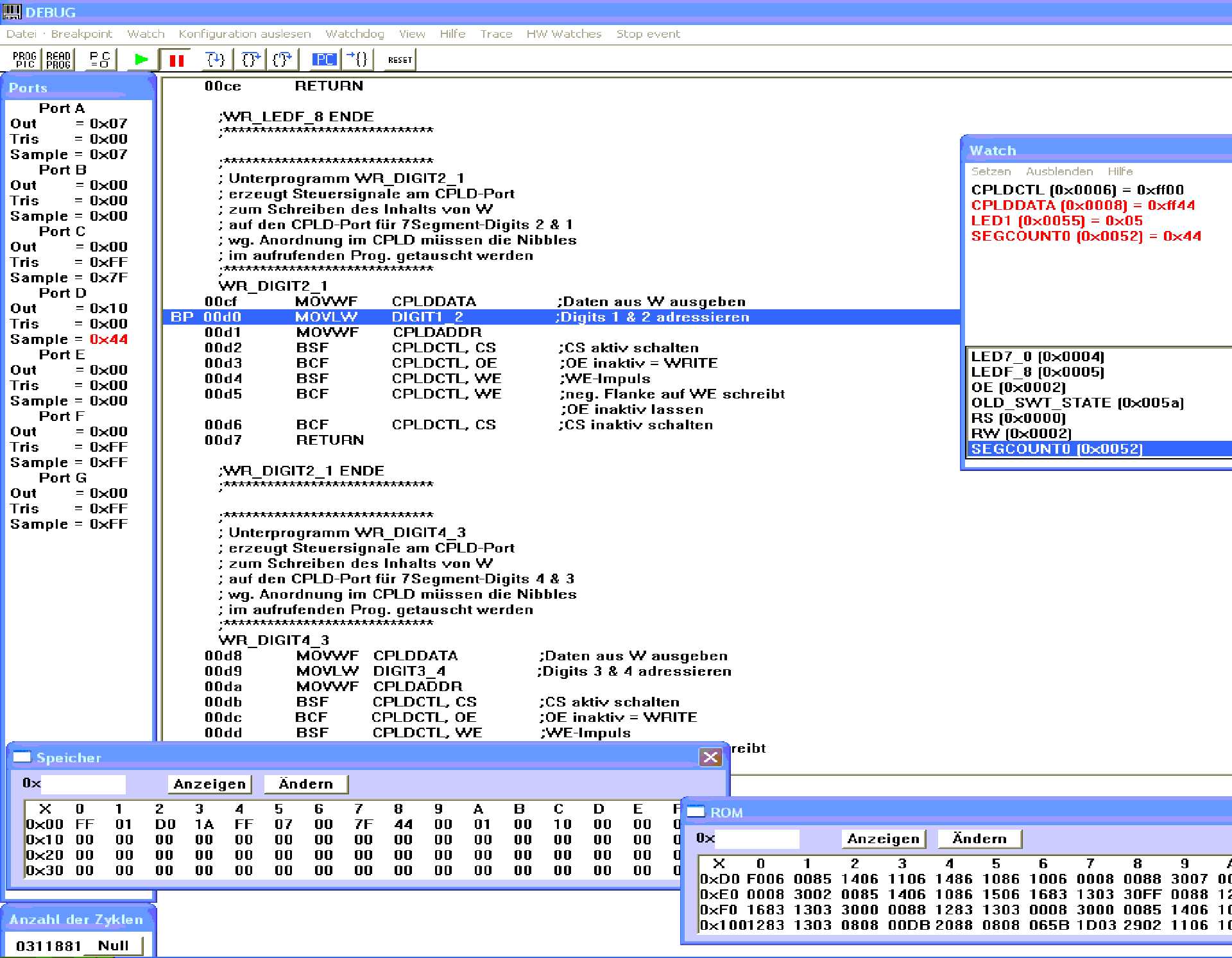

Es enstand auch eine komfortable Debugmöglichkeit für den entwickelten PIC-kompatiblen, synthetisierbaren Mikrocontrollerkern.

-

Das Debugsystem umfasst ein Hardwareinterface in VHDL, das im FPGA mit den entsprechenden Komponenten des Controllers kommuniziert, sowie eine PC-basierte Softwareapplikation, die dem Benutzer alle relevanten Daten aus dem Controller präsentiert und ihm die Möglichkeit gibt, auf bequeme Weise alle internen Funktionen zu kontrollieren.

-

Die Kommunikation zwischen Frontend und Backend des Debugsystems erfolgt über den JTAG-Port des FPGAs und belegt keinerlei Ressourcen des Mikrocontrollers.

-

Das Debugsystem, das über einfache Definitionen im Design aktiviert oder deaktiviert werden kann, erlaubt ein komfortables Debugging von Software für den FPGA-basierten Mikrocontroller. --> Paper auf dem IFAC Workshop 02/2006 ( Brünn)

Real-time Debugging mit Trace Buffer

- Mittlerweile (2007) verfügt das Debugsystem auch über einen flexibel konfigurierbaren Trace Buffer für Echtzeitaufzeichnungen. Komfortabel nutzbare Hardware Watches erlauben u.a. die effiziente Triggerung der Aufzeichnung von Daten im Trace Buffer (Paper).